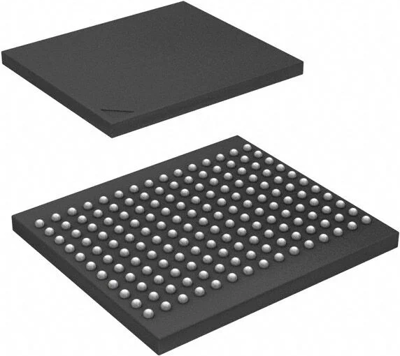

IS61NLP51236B-200B3LI | Integrated Silicon Solution INC

SRAM 18MBIT PAR 165TFBGA IS61NLP51236B-200B3LI

NCNR (non cancelable / non returnable)

State Bus Synchronous Sram, IS61NLP51236B-200B3LI, Integrated Silicon Solution INC

The 18Meg product features high-speed, low-power synchronous static RAM designed to provide a burstable, high-performance, 'no wait' state, device for networking and communications applications. It is organized as 512K words by 36 bits and 1024K words by 18 bits, fabricated with ISSI's advanced CMOS technology. Incorporating a 'no wait' state feature, wait cycles are eliminated when the bus switches from read to write, or write to read. This device integrates a 2-bit burst counter, high-speed SRAM core, and high-drive capability outputs into a single monolithic circuit. All synchronous inputs pass through registers are controlled by a positive-edge-triggered single clock input. Operations may be suspended and all synchronous inputs ignored when Clock Enable, /CKE is HIGH. In this state the internal device will hold their previous values.

Features

- No wait cycles between Read and Write

- Internal self-timed write cycle

- Individual Byte Write Control

- Single Read/Write control pin

- Clock controlled, registered address, data and control

- Three chip enables for simple depth expansion and address pipelining

- Power Down mode

- Common data inputs and data outputs

| Filter | Property | Value |

|---|---|---|

| Enclosure | TBGA-165 | |

| Assembly | SMD | |

| Memory size | 18 Mbit | |

| Voltage | 3.135-3.465 V | |

| Access time | 3 s | |

| Clock frequency | 200 MHz | |

| Technology | SRAM | |

| min. operating temperature | -40 °C | |

| max. operating temperature | 85 °C |

| Property | Value |

|---|---|

| Customs tariff number | 85423261 |

| MSL | MSL 3 |

| Country of origin | CN |

| Property | Value |

|---|---|

| SVHC free | Yes |

| Date of RoHS guidelines | 3/31/15 |

| RoHS conform | Yes |