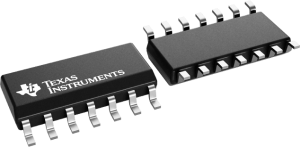

CD74HC73M | Texas Instruments

Dual JK-Flipflop, CD74HC73M, SOIC-14

As a private customer, you can buy this item as soon as we have it back in stock.

High Speed CMOS Logic Dual Negative-Edge-Triggered J-K Flip-Flops with Reset, CD74HC73M, Texas Instruments

The CD74HC73M is a high speed CMOS dual negative-edge-triggered J-K Flip-flop with reset. It utilizes silicon gate CMOS technology to achieve operating speeds equivalent to LSTTL parts. It exhibits the low power consumption of standard CMOS integrated circuits, together with the ability to drive 10 LSTTL loads It has independent J, K, Reset and Clock inputs and Q and Q\ outputs. It changes state on the negative-going transition of the clock pulse. Reset is accomplished asynchronously by a low level input. This device is functionally identical to the HC107 but differs in terminal assignment and in some parametric limits.

Features

- Hysteresis on Clock Inputs for Improved Noise Immunity and Increased Input Rise and Fall Times

- Asynchronous Reset

- Balanced propagation delay and transition times

- Complementary Outputs

| Output current | 5.2 mA | |

| Input voltage | 4.2 V | |

| Enclosure | SOIC-14 | |

| max. operating temperature | 125 °C | |

| min. operating temperature | -55 °C | |

| Assembly | SMD |

| Country of origin | MY |

| Customs tariff number | 85423390 |

| Original Packaging | Bar with 50 pieces |

| RoHS conform | Yes |

| Date of RoHS guidelines | 3/31/15 |

| SVHC free | Yes |